Software Specification

Version 3.0

Revision 1.1 July 20, 2009

www.docin.com

# Document Change History

| Revision | Date              | Responsible | Description of Change                                                                                                                                                                                                                                                                                                                     |  |

|----------|-------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1.0      | October 29, 2008  | LPL, SM     | Initial Release                                                                                                                                                                                                                                                                                                                           |  |

| 1.01     | December 19, 2008 | LPL, SM     | Overview: Specification 1.0.1 primarily corrects discrepancies between the released 1.0 SDK and the 1.0 specification. The 1.0 SDK already supports all items in spec 1.0.1 except added power state management options. No SIS or interface changes are required from SDK 1.0 to use existing 1.0 functionality.                         |  |

|          |                   |             | 2.5.1 Minor phrasing change due to addition of pre-P-<br>state change callback (see 4.3.7.4)                                                                                                                                                                                                                                              |  |

|          |                   |             | 2.5.2 Examples for use of slowdown input to module.                                                                                                                                                                                                                                                                                       |  |

|          |                   |             | 3.2.1 Typo and two outdated entries corrected in<br>MXM3_EFI_INTERFACE struct. Rest of document was<br>already correct in 1.0, struct now matches.                                                                                                                                                                                        |  |

|          |                   |             | 3.2.2 MxmReturnSpecLevel listed an EDID read function which did not exist in the 1.0 document. Removed, and renumbered the list entries to match.                                                                                                                                                                                         |  |

| 1//      |                   |             | 3.3.1 Typo (MXM_FUNC_EVENLIST) corrected. Typo in sample GUID for event 0x80 corrected (0xFB, should have been 0xF8 – this was already correct in the associated comment, the MXM_FUNC_EVENTLIST table, and the sample MOF. Updated sample code and MOF to include events 0xEF, 0xF0, and to remove event 0xD0 (see 4.3.7.1 and 4.3.7.2). |  |

| VV       | VV VV .           | $\cup$      | 3.3.2 & 3.3.2.1 Corrected values in sample code.                                                                                                                                                                                                                                                                                          |  |

|          |                   |             | 4.1.1 Changed BL value numbering on return when retrieving EDID to avoid conflict with MXM 2.x. Not used by SDK 1.0 VBIOS or tools.                                                                                                                                                                                                       |  |

|          |                   |             | 4.1.4 Changed register to return pointer to VBIOS, to more easily support blocks greater than 64K. Not used by SDK 1.0 VBIOS or tools.                                                                                                                                                                                                    |  |

|          |                   |             | 4.3.7.1 Replaced notification 0xD0 with 0xEF                                                                                                                                                                                                                                                                                              |  |

|          |                   |             | 4.3.7.2 Replaced notification 0xD0 with 0xF0. Clarified that SBIOS input on hotkey selection is optional.                                                                                                                                                                                                                                 |  |

|          |                   |             | 4.3.7.4 Added pre-P-state-change callback option to MXM_FUNC_MXCB. Added bits to return parameters to match the input parameters.                                                                                                                                                                                                         |  |

|          |                   |             | 4.3.7.5 Two 'future' section GUIDs updated (not used in existing spec). Replaced notify 0xD0 (notify for update of both MXPP and MXDP) with 0xEF and 0xF0 (notifies for updates of MXPP and MXDP respectively).                                                                                                                           |  |

| Revision | Date          | Responsible | Description of Change                                                                                                                                                                                                                                                                                                                                     |

|----------|---------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |               |             | Updated example to not reference 0xD0.                                                                                                                                                                                                                                                                                                                    |

|          |               |             | 5.2 Clarified DDC association for DVI-I. Added separate enumerations for the DP Aux ports in I2C field (0x9-0xC instead of all using 0x8 – already in SDK 1.0). Clarified link association in Digital Connection field.  5.5 Clarified use of PWR_LEVEL#. Added backward-compatible bit for GPIO-only power state select.                                 |

| 1.1      | July 20, 2009 | LPL, SM     | Overview: Specification 1.1 updates fields for new display standards, addresses possibly confusing references to uses of the PWR_LEVEL# pin, and reverts a DDC association made in release 1.0.1 which was not adopted in the MXM hardware specification. Existing implementations of the 1.0 and 1.0.1 specifications are not affected by these updates. |

|          |               |             | 2.5 and 5.5 Dropped references to alternate uses of<br>PWR_LEVEL# pin, this pin is intended solely to indicate<br>whether full power is or is not available.                                                                                                                                                                                              |

|          |               |             | 3.3.2 Corrected sample code references for ACPI version checking to compare to 0x300 instead of 0x30.                                                                                                                                                                                                                                                     |

| C        |               |             | 4.1.3 Clarified valid parameters for Boot Message System BLOS callback.4.3.7.4 Added new MXM_FUNC_MXCB callback options to support SBLOS notification on certain events. Since this is a new feature, it may not be supported by all GPU drivers.                                                                                                         |

|          |               | - 4         | 4.3.10.3 Extended external digital connector table entries for HDMI 1.2 to also apply to HDMI 1.3.                                                                                                                                                                                                                                                        |

|          |               |             | 4.3.10.3 Added DisplayPort 1.2 to list of types of external digital connectors.                                                                                                                                                                                                                                                                           |

| W        | $MMM_{\odot}$ |             | 4.3.10.4 Added eDP to list of types of internal flat panels.                                                                                                                                                                                                                                                                                              |

|          |               |             | 5.2 Added eDP to the list of Connector Types.                                                                                                                                                                                                                                                                                                             |

|          |               |             | 5.2 Default DDC association for DVI-I when using TMDS-over-LVDS moved to LVDS_DDC instead of VGA_DDC. MXM software should use the DDC field in the Output Device Structure to correctly support both old and new default assignments.                                                                                                                     |

# Table of Contents

| 1 | MXM Ve | ersion ( | 3.0 Software Overview                                            | 1  |

|---|--------|----------|------------------------------------------------------------------|----|

|   | 1.1.   | Softwa   | are Control of the MXM                                           | 1  |

|   | 1.1.1  | 1.       | MXM Advantage                                                    | 2  |

|   | 1.1.2  | 2.       | MXM Versioning and Interoperability                              | 3  |

|   | 1.1.3  | 3.       | MXM v 3.0 Interface Requirements                                 | 4  |

|   | 1.2.   | Softwa   | are Support for OEM Modules                                      | 5  |

|   | 1.3.   | MXM '    | VBI OS                                                           | 6  |

| 2 | The MX | M Syst   | em Information Structure                                         | 7  |

|   | 2.1.   |          | Header Structure                                                 |    |

|   | 2.2.   | MXM (    | Output Device Structure                                          | 7  |

|   | 2.2.   | 1.       | Sharing Display Output or DDC/Aux Lines Across System Connectors | 8  |

|   | 2.3.   | MXM S    | System Cooling Capability Structure                              | 9  |

|   | 2.4.   |          | Thermal Structure                                                |    |

|   | 2.5.   | MXM      | Input Power Structure                                            | 9  |

|   | 2.5.1  | 1.       | Auxiliary Power States                                           | 10 |

|   | 2.5.2  | 2.       | Changing Power States                                            | 11 |

|   | 2.     | 5.2.1.   | Asserting the Power State Pin (PWR_LEVEL#)                       |    |

|   | 2.     | 5.2.2.   | ACPI Notifications                                               | 11 |

|   | 2.     | 5.2.3.   | Examples                                                         | 12 |

|   | 2.6.   | MXM (    | GPIO Device Structure and GPIO Pin Entry Structure               | 14 |

|   | 2.7.   | MXM '    | Vendor Specific Structure                                        | 15 |

|   | 2.8.   | MXM I    | Backlight Control Structure                                      | 15 |

|   | 2.9.   | MXM I    | Fan Control Structure and Fan Speed Structure                    | 15 |

|   | 2.10.  | MXM (    | Checksum Byte                                                    | 16 |

| 3 | Core M | XM Sys   | stem Interfaces                                                  | 17 |

|   | 3.1.   | Requi    | red MXM Int15h System BIOS Callbacks                             | 17 |

|   | 3.1.1  | 1.       | Function 0 - Return Specification Support Level                  | 18 |

|   | 3.1.2  | 2.       | Function 1 - Return a Pointer to the MXM Structure               | 19 |

|   | 3.2    | Requi    | red MXM EFL System BLOS Callbacks                                | 19 |

|   | 3.2.1.        | EFI Interface                                                                | . 20 |

|---|---------------|------------------------------------------------------------------------------|------|

|   | 3.2.2.        | MxmReturnSpecLevel - Return Specification Support Level                      | . 21 |

|   | 3.2.3.        | MxmReturnStructure - Return Pointer to MXM Structure                         | . 21 |

|   | 3.3. Requi    | red MXM ACPI Methods                                                         | . 21 |

|   | 3.3.1.        | Accessing MXM ACPI Methods via WMI                                           | . 23 |

|   | 3.3.2.        | _DSM (Device Specific Methods)                                               | . 28 |

|   | 3.3.2.1.      | MXM_FUNC_MXSS - Return Supported Sub-Functions                               | . 30 |

|   | 3.3.2.2.      | MXM_FUNC_MXMI - Return Specification Support Level                           | . 31 |

|   | 3.3.2.3.      | MXM_FUNC_MXMS - Return MXM Structure                                         | . 32 |

| 4 | Additional MX | M System Interfaces                                                          | . 34 |

|   | 4.1. Additi   | onal MXM INT 15H System BIOS Callbacks                                       | . 34 |

|   | 4.1.1.        | Function 2 - Return a Pointer to the EDID Structure for the Internal Panel   | . 34 |

|   | 4.1.2.        | Function 3 – Select Output Device Channel                                    | . 35 |

|   | 4.1.3.        | Function 4 – Boot Message                                                    | . 36 |

|   | 4.1.4.        | Function 7 - Return a Pointer to the VBIOS Image for ROM-Less Adapters       | . 36 |

|   | 4.1.5.        | Function 8 - Check Availability of Output Device                             | . 37 |

|   | 4.1.6.        | Function 9 – Identify Output Devices                                         | . 37 |

|   | 4.2. Additi   | onal MXM EFI System BIOS Callbacks                                           | . 38 |

|   | 4.2.1.        | Returning the EDID Structure for the Internal Panel                          | . 38 |

|   | 4.2.2.        | MxmSelectOutputDevice - Select Output Device Channel                         | . 38 |

|   | 4.2.3.        | MxmCheckOutputDevice - Check Availability of Output Device                   | . 39 |

|   | 4.2.4.        | Return a Pointer to the VBIOS image for ROM-less Adapters                    | . 39 |

|   | 4.2.5.        | Identify Output Devices                                                      | . 39 |

|   | 4.3. Additi   | onal MXM ACPI Methods                                                        | . 40 |

|   | 4.3.1.        | Loading VBIOS image for ROM-less Adapters                                    | . 40 |

|   | 4.3.2.        | ACPI Notification                                                            | . 40 |

|   | 4.3.3.        | Returning the EDID Structure for the LVDS Panel via ACPI                     | . 40 |

|   | 4.3.4.        | Retrieving the Backlight Control Settings for the LVDS Panel via ACPI        | . 40 |

|   | 4.3.5.        | Check Availability of Output Device (Docking Stations and LID Display State) | . 40 |

|   | 4.3.6.        | Selecting the Display Output via ACPI                                        | . 41 |

|   | 4.3.7.        | _DSM (Device Specific Methods)                                               | . 42 |

|   | 4.3.7.1.      | MXM FUNC MXPP - Platform Policy                                              | . 42 |

| 4.3.7.2.        | MXM_FUNC_MXDP - Display Status              | 44 |

|-----------------|---------------------------------------------|----|

| 4.3.7.3.        | MXM_FUNC_MDTL - Display Toggle List         | 47 |

| 4.3.7.4.        | MXM_FUNC_MXCB - Query/Call System Callbacks | 47 |

| 4.3.7.5.        | MXM_FUNC_EVENTLIST                          | 49 |

| 4.3.8. M        | IXDS - Select Display Output Channel        | 51 |

| 4.3.9. M        | NXMX - Select Display Data Channel          | 52 |

| 4.3.10. Us      | lse of _DOD                                 | 53 |

| 4.3.10.1.       | Type 1 – VGA CRT                            | 55 |

| 4.3.10.2.       | Type 2 - Analog TV/HDTV Connector           | 56 |

| 4.3.10.3.       | Type 3 – External Digital Connectors        | 56 |

| 4.3.10.4.       | Type 4 – Internal Flat Panels               | 57 |

| 4.4. Serial R   | OM to Access the MXM v 3.0 Structure        | 57 |

| 4.4.1. A        | ccessing MXM ROM Via WMI                    | 58 |

| 5 MXM Structure | e Field Definitions                         | 59 |

| 5.1. MXM He     | eader Structure                             | 59 |

|                 | utput Device Structure                      |    |

| 5.3. MXM Sys    | stem Cooling Capability Structure           | 64 |

| 5.4. MXM Th     | nermal Structure                            | 64 |

| 5.5. MXM Inp    | put Power Structure                         | 65 |

| 5.6. MXM GP     | PIO Device Structure                        | 66 |

| 5.7. MXM Ve     | PIO Device Structure                        | 69 |

|                 | acklight Control Structure                  |    |

| 5.9. MXM Fai    | n Control Structure                         | 71 |

| Applicable Docu | ıments                                      | 73 |

# List of Figures

| Figure 1-1. | Non-MXM Software Combination Matrix Illustration | 2  |

|-------------|--------------------------------------------------|----|

| Figure 1-2. | MXM Software Illustration                        | 2  |

| Figure 1-3. | MXM Capabilities                                 | 3  |

| Figure 1-4. | MXM v 3.0 Software Compatibility                 | 3  |

| Figure 3-1. | Namespace with MXM Methods Example               | 22 |

# List of Tables

| Table 3-1.   | MXM_FUNC_MXSS Return Buffer               | 31 |

|--------------|-------------------------------------------|----|

| Table 3-2.   | MXM_FUNC_MXMI Return Buffer               | 32 |

| Table 3-3.   | MXM_FUNC_MXMS Structure Identifier        | 32 |

| Table 4-1.   | MXM_FUNC_MXPP Platform Policy             | 42 |

| Table 4-2.   | MXM_FUNC_MXPP Return Buffer Policy Status | 44 |

| Table 4-3.   | MXM_FUNC_MXDP Display Status              | 45 |

| Table 4-4.   | MXM_FUNC_MXDP Return Buffer Status        | 46 |

| Table 4-5.   | MXM_FUNC_MXCB Callback                    | 48 |

| Table 4-6.   | MXM_FUNC_MXCB Return Buffer Callbacks     | 48 |

| Table 4-7. ( | GUID List for Notification Codes          | 50 |

| Table 4-8.   | MXM Specific Fields in _DOD               | 54 |

| Table 4-9.   | Type 1 – VGA CRT                          | 55 |

| Table 4-10.  | Type 2 - Analog TV/HDTV Connector         | 56 |

| Table 4-11.  | Type 3 - External Digital Connectors      | 56 |

| Table 4-12.  | Type 4 – Internal Flat Panels             | 57 |

| Table 5-1.   | MXM Header Structure                      | 59 |

| Table 5-2.   | MXM Output Device Structure               | 60 |

| Table 5-3.   | MXM Output Device Structure               | 64 |

| Table 5-4.   | MXM Thermal Structure                     |    |

| Table 5-5.   | MXM Input Power Structure                 | 65 |

| Table 5-6.   | MXM GPIO Device Structure                 | 66 |

| Table 5-7.   | GPIO Pin Entry Structure                  | 67 |

| Table 5-8.   | GPIO Pin Usage Methods                    | 68 |

| Table 5-9.   | MXM Vendor Specific Structure             | 69 |

| Table 5-10.  | MXM Backlight Control Structure           | 70 |

| Table 5-11.  | MXM Backlight Frequency Structure         | 70 |

| Table 5-12.  | MXM Fan Control Structure                 | 71 |

| Table 5-13.  | MXM Fan Speed Structure                   | 72 |

# 1 MXM Version 3.0 Software Overview

#### 1.1. Software Control of the MXM

Key goals of the MXM v 3.0 software standard include interoperability of compliant MXM adapters and compliant MXM systems. An MXM adapter and its associated software (video BIOS and OS specific drivers) should work on any MXM compliant system without re-engineering of the module software or system software.

To achieve this, the MXM v 3.0 software standard defines a **System Information Data Structure** which resides on the system, and a standard set of software interfaces between the MXM adapter and MXM system (refer to the section MXM v 3.0 Interface Requirements to determine the minimum software requirements).

The MXM system information data structure defines the system configuration outside the MXM connector, including details such as:

| Display connectors               |

|----------------------------------|

| Cooling capability               |

| System power supply capabilities |

This MXM system information structure may be stored either in a separate I2C ROM on the motherboard, or in a data block within the system firmware (system BIOS, or SBIOS).

The MXM software interfaces provide methods to abstract control of functionality described in the system information structure. For example, display MUX steering and the consistent enumeration of display devices.

The module's VBIOS and driver software interpret the contents of the MXM v 3.0 structure and call the methods provided by the system to integrate the graphics module into the system. The SBIOS does not need to parse any data about the module, nor does it need to modify its behavior based on the particular module which is present. It simply stores the system information structure in binary form and reports it to the module when requested.

In this specification, the designer of the MXM module and its software are referred to as the "(graphics) vendor." The designer of the system and SBIOS is referred to as the "system designer."

Note: The MXM v 3.0 standard provides the foundation for interchangeable compliant modules. The SBIOS must not use specific properties, such as a module's PCI device ID, to alter features or behaviors defined via the MXM standard.

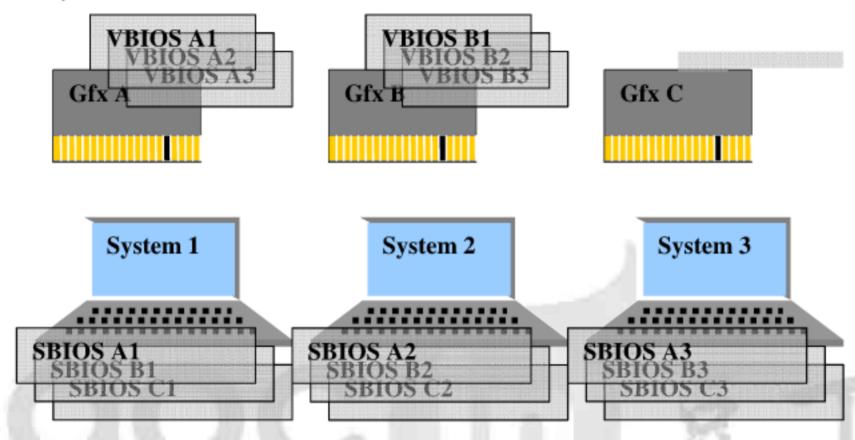

## 1.1.1. MXM Advantage

The MXM software standard provides a substantial benefit in terms of flexibility, maintenance, and inventory control. Without standardized interfaces, a unique VBIOS containing system specification settings must be generated for every module and system combination (X\*Y unique VBIOSes). The same may be true for the SBIOS.

Figure 1-1. Non-MXM Software Combination Matrix Illustration

With an MXM compliant module and platform, a single VBIOS per module type and a single SBIOS (with system information) per system type is sufficient. The graphics software combines this information at runtime.

Figure 1-2. MXM Software Illustration

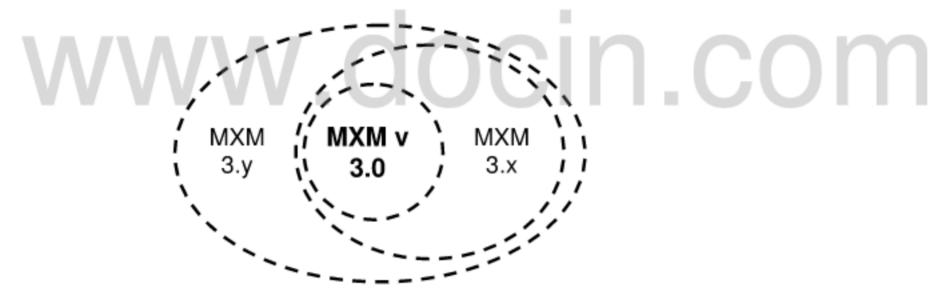

## 1.1.2. MXM Versioning and Interoperability

When an MXM adapter is installed into a system, the resulting system capabilities are the intersection set of the MXM adapter and the base platform. Only the capabilities that are present in both will be available. For example, if (A) the MXM module supports the High-Definition Multimedia Interface (HDMI<sup>TM</sup>) output technology and (B) the base platform supports routing HDMI to an HDMI connector, then that likely means that HDMI can be supported. However, if the base platform (including dock) did not have an HDMI connector then no HDMI capability should be expected regardless of the MXM module's capabilities.

Figure 1-3. MXM Capabilities

Both the MXM adapter and the base platform convey software version information indicating the highest level of the MXM v 3.0 software interface that each supports. Between the MXM v 3.0 software interfaces, backwards compatibility within a major version is required. For example, a 3.x platform shall support any adapter 3.x ~ 3.0. Backwards compatibility with MXM v 2.x and 1.x is not required. Forward compatibility is not required. However, all structures and members, within later revisions (3.y) will remain backward compatible with previous 3.x implementations.

Figure 1-4. MXM v 3.0 Software Compatibility

### 1.1.3. MXM v 3.0 Interface Requirements

The following requirements are intentionally minimal. The system does not need to interpret anything about the module capabilities. The module software must have access to certain pieces of information and interfaces, both before driver load (typically pre-OS operation where the VBIOS is responsible for graphics functionality, where Int15h and EFI interfaces are used) and after the driver is present (where the ACPI interfaces are in effect). Functionality must also consider the needs of MXM adapters. They may need to operate as secondary display adapters (VGA resources are disabled, or it is enumerated as a non-VGA device) when the VBIOS interfaces may not be available. Both Int15h/EFI and ACPI interfaces are required. These are required even if the MXM module is not the primary VGA device. Refer to the following sections for descriptions on the Int5h/EFI and ACPI system methods.

- MXM v 3.0 INT 15H System BIOS Callbacks

- MXM v 3.0 EFI System BIOS Callbacks

- MXM v 3.0 ACPI Methods

MXM modules may contain either legacy (non-EFI) VBIOSes or hybrid EFI/legacy VBIOSes. If legacy operating system support is needed, the VBIOS and SBIOS must provide legacy interfaces.

The following summarizes the required software support:

- Setting Subsystem Vendor and Device ID. The SBIOS should set the module's subsystem information to the desired value. The specific registers to set may vary by graphics processing unit (GPU). Consult graphics vendor-specific documentation.

- MXM Structure for each MXM connector

- Header and Checksum are required

- At least one Output Device substructure (if the adapter has an output)

- Cooling capability substructure

- At least one Input Power substructure

- An interface to obtain the MXM structure from the system. Typically, this is a software interface. Less commonly, the MXM structure can be stored in a platform-resident ROM (only one of the two approaches is needed).

- Int15h Func 0 / EFI MxmReturnSpecLevel and Int15h Func 1 / EFI MxmReturnStructure

- ACPI\_DSM method subfunctions MXM\_FUNC\_MXSS, MXM\_FUNC\_MXMI and MXM\_FUNC\_MXMS

Additional items may be required depending on the system features. Following examples are:

- Backlight substructure if GPU PWM backlight is used

- GPIO substructures if module GPIOs are used

- Int15h Func 2 / EFI standard EFI\_EDID\_OVERRIDE\_PROTOCOL and the \_DDC standard ACPI method if a non-DDC internal flat panel is used

- Int15h Func 3 / EFI MxmSelectOutputDevice and the MXMX & MXDS ACPI methods if a Display DDC or Output MUX is used with system methods.

Unless otherwise noted, structures and methods not listed are optional and not required.

The MXM structure is static. It is created once during platform design (with the help of the MXMedit tool) and does not change based on the current operating mode of the system. Parsing of the MXM structure is required only by the GPU software.

Since the GPU software must be active in order to request and parse MXM information, behavior requested by the system in the MXM system information structure will not take effect until the software has initialized. This includes thermal and power information. In addition, due to VBIOS limitations full functionality may not be available until the GPU software driver loads during OS initialization.

Compliant MXM adapters which, on boot, detect that an MXM System Information Structure is not present must assume they are operating on a non-compliant system. The module must ensure safe operation in a minimal configuration safe-mode. This includes booting on the CRT only, in the lowest possible performance state with lowest possible thermal and input power burden. The use of warning messages by the module, at POST or OS boot, to indicate mis-configuration, is strongly encouraged.

# 1.2. Software Support for OEM Modules

The MXM v 3.0 standard allows for OEMs to create limited variants outside the core MXM standard in order to add features or optimize cost. The platforms must also be capable of supporting a fully MXM compliant module.

Such deviations from the specification, such as additional power rails, require no software support. The use of a VBIOS image merged with the SBIOS on a single ROM on the platform does not change the behavior of the MXM module software.

### 1.3. MXM VBIOS

The VBIOS for an MXM compliant module should be stored in a ROM on the MXM v 3.0 graphics module (in the same manner as VBIOSes are stored for desktop cards). OEM modules can instead store the VBIOS in the SBIOS in a single non-volatile storage device on the motherboard.

Systems which are MXM compliant shall support MXM compliant modules. Any modules with a VBIOS in on-module ROM will override the VBIOS in the system. For modules without a ROM, during POST the VBIOS will check if it is running on the adapter it was built for (for example, by checking Device ID) and fail POST if it is not correctly matched.

The MXM VBIOS is fully VESA compliant and operates in the same fashion as non-MXM VBIOSes. Some vendor-specific extensions may also be available. However, use of these extensions should be avoided in order to facilitate cross-vendor module compatibility.

Refer to the MXM v 3.0 Interface Requirements section for interface and operational requirements.

# 2 The MXM System Information Structure

The MXM v 3.0 structure consists of a mandatory header structure followed by a variable number of substructures and a mandatory checksum byte. Data is assumed to be in little endian format.

Systems may have more than one MXM connector, so they may store more than one MXM structure. The software interface supports specifying which connector data is being requested for. Data in MXM structures is specific to a particular system configuration (for example, which connectors are present on a particular model of the system, which MXM slots are currently stuffed, etc.), so an SBIOS may store multiple version of the MXM structures and report them based on the particular model and configuration of the system.

The MXM structure for a system is created through a simple editing tool (available as part of the SDK). The MXM structure is stored in the SBIOS and is requested by and parsed by the module software. The exact bit-level contents of the structure are generally of interest only to graphics vendors and not system designers. Usage is summarized here and bit level details are provided at the end of this specification in Chapter 5.

## 2.1. MXM Header Structure

The MXM header identifies the version of the system information structure stored. Currently only one version is available (3.0), but in the future systems may, if desired, store MXM structures for multiple MXM module versions. If no exact match is available, the MXM software will determine the best mapping between itself and the available structure version.

Refer to Table 5-1 for a description of the header at the beginning of the MXM structure.

# 2.2. MXM Output Device Structure

Each output device structure describes a single display connector or integrated display. There will be multiple MXM output device structures in the MXM structure, defining one output device each.

An output device shall be enumerated for each supported integrated display and display connector. For example, each DVI output that can be routed to either an onboard connector or a docking connector must have one dedicated output device structure for each connector. In the case of a DVI-I output connector there are separate output device structures for the analog and digital outputs.

Any MXM module which outputs to a display device will therefore require one or more output device structures. Some MXM modules, such as secondary MXM modules in multi-GPU configurations, may have no output device structures.

The ordering of output devices implies the default boot device, and the detection order. For example, the first output device is the default boot display device. The second output device will be the boot display device if the first is not attached. The third if the second is not attached, and so on.

Refer to Table 5-2 for a description of the MXM Output Device Structure.

## Sharing Display Output or DDC/ Aux Lines Across System Connectors

If a system requires more display outputs or DDC/Aux lines than the MXM adapter provides, it may need to use on-system MUXes to share signals. The display outputs and DDC/Aux lines must be controlled separatel. For example, a single MUX control cannot be used to switch both the output and the DDC/Aux lines. DDC/Aux lines also cannot be shared by attempting to put them all on a single bus without isolating them via a MUX (some external display devices can interfere with one another if connected on a shared bus, making it impossible to communicate properly unless they are isolated properly.).

Note: In the MXM specification, MUX control can be done either through direct GPIO control from the module (the signals to control the MUX are routed directly to the GPIO pins on the MXM connector, and defined in the GPIO structures) or through a defined interface to the SBIOS (the signals to control the MUX are handled by the platform in response to calls from the MXM graphics software to the SBIOS).

If signal control direct from the module is used:

- Display output MUX control must be implemented as a 2:1 switch. The use of this control must be indicated in the Output Device Structure, and the GPIO used must be described in the GPIO Device Structure. The associated MXM connector GPIO and the state of that GPIO in order to select the output must be provided.

- DDC/Aux line control must be implemented as a n:1 switch. Each connector will have an associated GPIO identified in the Output Device Structure and the GPIO Device Structure. When this GPIO is asserted, the GPU can communicate with the device.

# 2.3. MXM System Cooling Capability Structure

The MXM System Cooling Capability Structure defines the thermal power dissipation capability of the MXM thermal solution contained in the system. This structure is **required** for all MXM systems. The maximum performance level of the MXM module will be determined by the lowest of its cooling capability and its current input power.

Refer to Table 5-3 for a description of the MXM Cooling Capability Structure.

### 2.4. MXM Thermal Structure

The MXM v 3.0 module hardware and software will regulate its own temperature by varying the performance of the GPU. The **optional** thermal structures allow the system to specify its own thermal requirements. There can be up to one thermal structure of each type as described.

- Maximum temperature: If the system requires the module maintain a lower maximum temperature than the module default, an MXM thermal structure can specify this information in terms of GPU junction temperature. The MXM module hardware and software will ensure the module meets the system's stated requirements.

- Alert signals: The TH\_ALERT pin output from the module indicates a high (but not critical) temperature, which may for example be used by the system as a signal to enable a higher system fan speed. The system can specify the temperature at which this pin should assert.

Note: The TH\_OVERT pin is a separate connector pin which indicates a critically high module temperature (at which shutdown of the module is recommended). This temperature is determined by the module and therefore cannot be specified by the system. If this temperature is exceeded at any time, including power-on, the system must shut down the module immediately to prevent damage.

Refer to Table 5-4 for a description of the MXM Thermal Structure.

# 2.5. MXM Input Power Structure

The MXM Input Power Structure defines the maximum continuous available input power provided by the system for the PWR\_SRC input power rail. At least one power structure is required. An additional MXM input power structure is required for each platform supported power level for the MXM module. Typically there will be either one structure (which then applies globally) or two (one for AC and one for battery operation).

The maximum performance level available to the MXM module will be determined by the lowest of its cooling capability and its current input power. MXM modules generally contain a limited number of pretested operating power states, from which the module software selects an appropriate level that

is equal to or less than the system's current power budget. Due to the limited number of module levels, small changes to the MXM structure information may cause substantial changes in available performance. For example, if a module contains 30 W, 35 W and 40 W performance levels, a 35 W system power will result in a 35 W module power state. Changing the system power to 36 W will have no change in graphics performance, while changing it to 34 W would require the module to reduce its power consumption to 30 W.

When first powered on, until it can read the MXM system information, the module should operate in a low power state. At software initialization, GPU software can read the module and system capabilities. The GPU software initialization may fail if the lowest module P-state exceeds the current system power budget for the module.

Refer to Table 5-5 for a description of the MXM Input Power Structure.

### 2.5.1. Auxiliary Power States

Some systems may require more than the two standard power states (AC and battery). For example, a system may support a light-weight power-brick that is AC connected but cannot support operation at the same full performance as the normal AC state. Or it may possess a higher capability docking station that allows operation at higher states than normal AC and battery operation.

If auxiliary power states are defined, they behave like static performance limits such as those defined for the PWR\_LEVEL# signal. They define additional states wherein the module performance is limited by the MXM software (through the use of voltage, frequency or other limiting mechanisms) to ensure the maximum power consumed by the module always remains within the specified limit.

Entry into a particular power level is triggered via corresponding **ACPI Notify Code**. Notification codes 0xD1~0xD5 represent P0~P4 respectively. P0 is the default operating mode, representing no auxiliary power state restriction.

Auxiliary power states are intended for system state changes such as the power supply changes as previously described. Use of such states requires a GPU driver to be active. Fine-grained runtime power control should not be assumed by the system through this mechanism.

Constraint to a new power limit does not occur immediately when the notifier is issued. The transition is not required to complete within any consistent time interval, and may vary depending on system demands or quality of service constraints. This mechanism should therefore not be used for critical power control (for example, for thermal control). The module can provide an optional callback at the start and end of the power state transition if the system needs to know when the new power limit has been met (this usage is outlined in the section *Changing Power States.*).

These limits do not imply operation at a specific power or clock level -- the module may operate at any performance level which meets the specified power limit.

### 2.5.2. Changing Power States

Many systems can provide the same level of power to the graphics module regardless of operating conditions. In this case, no action is needed. However, for designs where control of module power is required (such as notebooks which can supply less power to the module during battery operation), several options are available.

Power restrictions from the system may occur due to tuning preferences by the system or due to external events such as the system being disconnected from AC power.

If a system supports only one module power state, only one input power structure will exist (with the **Type** set to 1).

See Section 5.5 for the bit field definitions of the Input Power Structure.

## 2.5.2.1. Asserting the Power State Pin (PWR\_LEVEL#)

Asserting PWR\_LEVEL# is required in all cases when a power state transition is due to a drop in the available power to the module. This provides the opportunity for the module to respond immediately, without waiting on software notifications. Asserting is not required for power state transitions caused by an increase in available power or a decrease requested for reasons other than power availability (such as entering a power saving operating mode).

Note: If the PWR\_LEVEL# input pin is asserted on the module, then regardless of other requirements or SBIOS power state requests, the module must restrict power consumption to power specified in the Input Power Structure with Type 0. As described, this hardware induced power consumption change may be used as an interim 'safe' state during power level transitions, or as an end state.

If the PWR\_LEVEL# pin will stay asserted for the duration while at input power level Type 0, that input power structure must set the notification type bit to 1. Otherwise it is expected that the pin will only be asserted during the transition (as outlined in the examples in Section 2.5.2.3).

If the system has no ACPI mechanisms implemented, at most two power levels can be supported (Type 0 and Type 1). Power selection must be done entirely off the PWR\_LEVEL# pin. The ACPI type field should be set to 1 to indicate this system method.

### 2.5.2.2. ACPI Notifications

If input power levels 0 and 1 are defined, the system is assumed to support the standard ACPI notebook power state notification (with level 0 indicating the battery power level).

If any auxiliary power states are defined, the system is assumed to support MXM ACPI Auxiliary Power State notifications. The MXM ACPI notifiers (one or more of 0xD1-0xD5) must be implemented.

These two notification methods set separate thresholds. The MXM driver must select the lower of the two if both are in effect. For example, if a system is running on battery power and the SBIOS also requests the module limit power to Auxiliary Power Level 1 (Input Power Structure Type 0x9), the lower of the two limits applies.

## 2.5.2.3. Examples

The interaction of these mechanisms offers a range of options to the system, as illustrated.

- □ Example 1: Basic power supply transitions (AC and battery) only

- Setup requirements:

- a) PWR\_LEVEL# should be connected to power supply or similar output to assert while running on battery.

- b) MXM input power structure: battery level power entry (entry with Type 0) should set the Hardware Notification field to '1'.

- c) No callbacks are required.

- Runtime operation: on switching to battery power:

- a) System asserts PWR\_LEVEL# pin on transition to battery power.

- Adapter restricts power consumption to Input power structure of Type 0 (battery level).

- c) SBIOS issues standard ACPI power source notification (battery mode)

- d) GPU driver receives request and may perform additional module power state adjustments. Power consumption remains restricted to the battery power level.

- Runtime operation: on switching to full power:

- a) System de-asserts PWR\_LEVEL# pin on transition to AC power.

- MXM adapter is free to resume operation at the AC power level.

- c) SBIOS issues standard ACPI power source notification (AC mode)

- Driver receives request and may perform additional module power state adjustments.

#### Example 2: Additional software controlled power states

Some systems may use additional power states selected by the SBIOS using the MXM auxiliary power notifications.

- Setup requirements:

- a) MXM input power structure: power state Type 0 (only) may set the Notification Type field to '1' (as appropriate for system behavior).

- b) PWR\_LEVEL# must be connected to a power supply signal or under software control (as explained).

- c) If the system supports an auxiliary power state or PWR\_LEVEL# will not stay asserted while in power state Type 0, the SBIOS must support the MXM\_FUNC\_MXCB post-power state change callback (and should indicate this during the initialization time MXM\_FUNC\_MXCB support check performed by the MXM driver).

#### Runtime operation:

- a) System asserts PWR\_LEVEL# pin if required (see Section 2.5.2.1)

- b) If PWR\_LEVEL# asserts, adapter restricts power consumption to input power structure of Type 0.

- c) SBIOS issues ACPI notification (standard ACPI power source notification, or MXM auxiliary power state notification) for desired state.

- d) Driver receives request and performs any needed module power state changes. The new limit is the min based on the current power source and the current auxiliary power state. On completion, driver issues MXM\_FUNC\_MXCB post-power state change callback.

- e) If PWR\_LEVEL# was asserted, and will be de-asserted for this power state, SBIOS must wait till MXM\_FUNC\_MXCB callback before de-asserting.

### □ Example 3: Systems requiring per-module power state control

If a system wishes to control the power level of multiple MXM modules, it can use the same mechanism as previously described as long as the same power state will be set across all modules. However, if the system wishes to set different modules to different power levels, the SBIOS must support the pre-power state change MXM\_FUNC\_MXCB callback. This is to ensure proper communication of desired power levels even in cases such as WMI notifiers (which, unlike direct notifiers, are not module specific). If this callback is not supported, it is assumed by the module software that the same power state is desired for all modules.

#### Setup requirements:

- a) MXM input power structure: power state Type 0 (only) may set the Notification Type field to '1' (as appropriate for system behavior).

- PWR\_LEVEL# must be connected to a power supply signal or under software control (as futher explained).

- c) If the system supports an auxiliary power state or PWR\_LEVEL# will not stay asserted while in power state Type 0, the SBIOS must support the MXM\_FUNC\_MXCB post-power state change callback (and should indicate this during the initialization time MXM\_FUNC\_MXCB support check performed by the MXM driver).

- d) SBIOS should support the MXM\_FUNC\_MXCB pre-power state change callback (and should indicate this during the initialization time MXM\_FUNC\_MXCB check).

#### Runtime requirements:

- System asserts PWR\_LEVEL# pin on all modules if required (see Section 2.5.2.1).

- b) If PWR\_LEVEL# asserts, each adapter restricts power consumption to input power structure of Type 0.

- c) SBIOS issues ACPI notification (standard ACPI power source notification, or MXM auxiliary power state notification) for desired state.

- d) Driver receives request and may call SBIOS via MXM\_FUNC\_MXCB pre power state change callback to verify desired power level on each GPU.

- e) Driver receives request and performs any needed module power state changes. The new limit is the min based on the current power source and the current auxiliary power state. On completion, driver issues MXM\_FUNC\_MXCB post-power state change callback.

- f) If PWR\_LEVEL# was asserted, and will be de-asserted for this power state an SBIOS must wait until MXM\_FUNC\_MXCB callback before deasserting.

Refer to the section on the MXM\_FUNC\_MXCB callback function for details on the MXM notification.

Note:

With these mechanisms the system is imposing a power limit on the module. This may not correspond to a change to a specific GPU clock level since power may be limited in other ways. Or since the module is free to select power levels at or below the current limit at any time, it may already be operating at a sufficiently low power level so no clock changes or other changes will be visible. The MXM\_FUNC\_MXCB callback calls must still be performed by the module software in order to confirm that sufficient action has been taken.

Power state transitions may occur for reasons other than the current system request. A system waiting for a requested transition to complete should not assume that the next callback received is a response to its requested action. It should specifically check that the specified P-state is at or below the system requested level (before proceeding, for example, with de-asserting the PWR\_LEVEL# pin).

# 2.6. MXM GPIO Device Structure and GPIO Pin Entry Structure

This structure applies to standard module-provided GPIOs, provided on the MXM connector. The structure is optional, and it is only needed if the system uses one or more MXM module GPIOs. GPIOs are described with a list of **GPIO Device Structures** and **GPIO Pin Entry Structures**. Each GPIO device description is followed by one or more GPIO pin description for pins on that device.

An MXM GPIO Device Structure is used to define whether the MXM Physical & Logical GPIO pins are attached to the pre-defined module GPIOs, or to OEM defined GPIOs.

The MXM GPIO Pin Entry Structures follow the GPIO Device Structure and enumerate the function and usage of all the MXM GPIO pins used.

Refer to Table 5-6 a description of the MXM GPIO Device Structure and Table 5-7 for the MXM Pin Entry Structure.

The Logical pin number referenced in other data structures such as the Output Device Structure is determined by numbering the GPIOs beginning with '0' for the first direct GPIO pin on the module connector up to the total number of direct GPIOs.

Refer to the MXM Version 3.0 Graphics Module Thermal Electromechanical Specification for the GPIO function hardware definitions.

# 2.7. MXM Vendor Specific Structure

This is an optional GPU vendor specific structure (VSS). The contents of the structure are defined by the vendor, where each structure is tagged to indicate to which vendor it applies. There may be multiple structures, for example, with one VSS per supported vendor. Contact the GPU vendor for any additional details on VSS requirements or contents.

Refer to Table 5-9 for a description of the general format of the MXM Vendor Specific Structure. Specific details of any VSS data will be provided separately in vendor specific documentation.

# 2.8. MXM Backlight Control Structure

This is an optional field that describes the settings for the LCD panel integrated into the chassis. If no PWM or I2C based LCD inverter is supported then the field is not required.

The table provides only the hardware information the GPU software requires in order to set a requested brightness. The interface by which brightness requests are communicated (for example, for brightness control hotkeys) is a separate topic outside the scope of the MXM standard. The Windows Vista operating system, for example, supports ACPI 3.0 standard ACPI notifiers and methods for this purpose. The OS provided control software in turn calls the GPU software to set the requested brightness value.

Refer to Table 5-10 for a description of the MXM Backlight Control Structure.

# 2.9. MXM Fan Control Structure and Fan Speed Structure

This optional structure applies to an MXM module-controlled system fan, if present. The MXM module provides a PWM output for this purpose.

Fan control is described with a Fan Control Structure and one or more Fan Speed Structures. The Fan Control Structure describes the physical properties of the fan. The Fan Speed Structures specify temperature thresholds and fan speeds to describe the expected behavior the module should implement.

Refer to Table 5-11 for a description of the MXM Fan Control Structure and Table 5-12 for the MXM Fan Speed Structure.

# 2.10.MXM Checksum Byte

The MXM checksum byte is the two's complement of the 8-bit sum of the entire MXM v 3.0 structure (including header but not the checksum itself) and is the last byte in the MXM table.

# 3 Core MXM System Interfaces

All MXM systems must provide access to the MXM System Information Structure. This can be done either via software interfaces or through a ROM on the motherboard that is directly accessible by the MXM module.

In most cases the same software functionality is mirrored in an Int15h, EFI, and ACPI version. The ACPI version is required, as the Int15h version. The EFI version is required for EFI compliant SBIOSes only.

Chapter 4 discusses additional system interfaces which may be needed depending on system design choices.

# 3.1. Required MXM Int15h System BIOS Callbacks

A set of SBIOS callback functions has been defined in order to allow the communication of system information between the VBIOS and the SBIOS.

If the SBIOS does not support a described callback, then when called it should return with a value other than 005Fh in AX.

| Note: | In some instances below, one of the parameters is the 'Adapter ID', used to differentiate which |

|-------|-------------------------------------------------------------------------------------------------|

|       | MXM module is being referenced. This is a 16-bit value constructed as follows from the PCI bus  |

|       | information                                                                                     |

Bits [15:8] Bus

Bits [7:3] Device

Bits [2:0] Function

An adapter ID of '0' is acceptable when referring to the primary GPU in the system (that is, the one whose VBIOS is POSTed at system boot).

The ability to access secondary adapter information without a driver is primarily needed to enable test applications.

## Function 0 – Return Specification Support Level

This is a required function that allows the VBIOS to get information from the SBIOS about the level of the MXM software specification that the system supports, and the support information for individual functions.

#### Entry:

AX = 5F80h

BL = 00h

BH = FFh

EBX[16:31] = Adapter ID (see above)

CX = Revision of the MXM software specification that is supported by the MXM module

Format is binary coded decimal, for example: 0030h = 3.0, etc.

#### Return:

AX = 005Fh to indicate that the system bios supports this function

BL = Revision of the MXM software specification that is supported by the system

Format is binary coded decimal, for example: 30h = 3.0, etc.

CX = MXM functions supported

Bit 0 = 1

Bit 1 = 1 if Function 1 is supported, 0 if not supported

Bit 2 = 1 if Function 2 is supported, 0 if not supported

Bit 3 = 1 if Function 3 is supported, 0 if not supported

Bit 4 = 1 if Function 4 is supported, 0 if not supported

Bit 7 = 1 if Function 7 is supported, 0 if not supported

Bit 8 = 1 if Function 8 is supported, 0 if not supported

Bit 9 = 1 if Function 9 is supported, 0 if not supported

#### 3.1.2. Function 1 – Return a Pointer to the MXM Structure

This is a required function that will return a pointer to the MXM structure, which is stored in the SBIOS ROM area or some other memory location which is accessible in real mode during video POST.

#### Entry:

AX = 5F80h

BL = 01h

BH = FFh

EBX[16:31] = Adapter ID (see above)

CX = Identifier for the data block to return

To obtain the MXM information structure, use CL to specify the revision of the MXM software specification that is supported by the MXM module. Format is binary coded decimal, for example: 0030h = 3.0, etc.

To obtain an additional vendor specific data block, use CL to specify an identifier in the range 0x80-0x8F. If the system BIOS does not contain such a data block, it should return an error in AX. Graphics vendors should not assume a specific assignment within this range – the SBIOS can store the data for different vendors in any order in the 0x80-0x8F identifier range.

Details for any such OEM or graphics vendor specific data blocks are outside the scope of this document.

#### Return:

AX = 005Fh to indicate that the system bios supports this function

BX = Vendor ID of data block if CX = 0x80-0x8F, else 0

ES:DI = Pointer to the MXM structure in real mode memory (< 1MB)

# 3.2. Required MXM EFI System BIOS Callbacks

A set of SBIOS callback functions has been defined in order to allow the communication of system information between the VBIOS and the systems supporting the Extensible Firmware Interface (EFI).

Refer to Section 1.1.3 (MXM v 3.0 Interface Requirements) for a summary of interface and operational requirements.

#### 3.2.1. EFI Interface

The GUID defined for the EFI interface.

```

#define MXM3_EFI_GUID {4EA9D4FE-E6F6-410b-8037-0F98B5968B65}

```

The interface itself is as follows:

#### Note: ControllerHandle and ChildHandle

In some instances below, one of the parameters is the handle 'ControllerHandle', used to differentiate which MXM module is being referenced. This is the EFI handle for the PCI device. 'ChildHandle,' where used, is the output device (the display).

usStructSize

usStructSize is set to the size of the supplied buffer by the caller, and on return should contain the actual size of the structure. If the structure is larger than the buffer, EFI\_BUFFER\_TOO\_SMALL should be returned as the status of the call.

Any unsupported function should return a status of EFI\_UNSUPPORTED. Bad input parameters such as an invalid handle should return EFI\_INVALID\_PARAMETER. Passing too small a buffer should return EFI\_BUFFER\_TOO\_SMALL. A successful call should return EFI\_SUCCESS.

## 3.2.2. MxmReturnSpecLevel – Return Specification Support Level

Caller provides pointer to location, which on call contains the module requested specification revision level, and which on exit, will contain the platform's preferred revision level and bit field of supported functions.

```

typedef EFI_STATUS (EFIAPI *MXM_RETURN_SPEC_LEVEL) (

IN struct _MXM3_EFI_INTERFACE *This,

IN         EFI_HANDLE ControllerHandle,

INOUT UCHAR16 usStructSize,

INOUT UCHAR8 *pucRevisionLevel,

OUT UINTN *puSupportFuncs

);

```

Where the integer value passed in uSupportFuncs indicates supported functions:

```

Bit 0 = '1' (this method is required)

```

Bit 1 = '1' (MxmReturnStucture is also required)

Bit 2 = '1' if MxmSelectOutputDevice is supported, '0' if not

Bit 3 = '1' if MxmCheckOutputDevice is supported, '0' if not

Other parameters follow the definitions in the Int15h interface, function 0.

### 3.2.3. MxmReturnStructure – Return Pointer to MXM Structure

Caller provides expected MXM interface revision level and a pointer which, on return will contain the MXM structure.

```

typedef EFI_STATUS (EFIAPI *MXM_RETURN_STRUCTURE) (

IN struct _MXM3_EFI_INTERFACE *This,

IN EFI_HANDLE ControllerHandle,

INOUT UCHAR16 usStructSize,

IN UCHAR16 usDataBlockID,

OUT CHAR8 *pMxmStruct

);

```

Input parameters follow the definitions in the Int15h interface, function 1.

# 3.3. Required MXM ACPI Methods

Where supported, methods within the ACPI namespace of the graphics adapter provide access to platform specific MXM functionality known by the SBIOS. Refer to implementation specific documentation on ACPI video extensions (Advanced Configuration and Power Interface Specification Revision 3.0a) for additional details.

Refer to the MXM v 3.0 Interface Requirements for interface and operational requirements.

Figure 3-1 is an overview of the altered and new methods in the namespace (affected methods are **bold** type). (This includes optional methods described in Chapter 4.)

```

I- PCI

- WMI1

// WMI Device

// WMI Method wrapper

I — WMMX

// Define the VGA controller in the namespace

- VGA

// Method to control display output switching

- DOS

|- _DOD

// Method to retrieve info on child output devices

|- _ROM

// Method to retrieve the ROM image for this device

- DSM

// Method for probing MXM Support and calling MXM

|- CRT

// Child device CRT

|- _ADR

// Hardware ID for this device

|- _DCS

// Get current hardware status

|- _DGS

// Query desired hardware active \ inactive state

|- _DSS

// Set hardware active \ inactive state

MXMX

// Method for selecting display data channel

MXDS

// Method for selecting display output

// Child device HDMI

- HDMI

// Hardware ID for this device

|- _ADR

// Get current hardware status

I- _DCS

// Ouery desired hardware active \ inactive state

|- _DGS

// Set hardware active \ inactive state

|- DSS

- MXMX

// Method for selecting display data channel

- MXDS

// Method for selecting display output

// Child device LCD

// Hardware ID for this device

- _ADR

|- _DDC

// Get EDID information from the monitor device

- _DCS

// Get current hardware status

- _DGS

// Query desired hardware active \ inactive state

- _DSS

// Set hardware active \ inactive state

- BCL

// Brightness control levels

// Brightness control method

|- _BCM

// Child Device TV

// Hardware ID for this device

- _ADR

// Get EDID information from the monitor device

DDC

_DCS

// Get current hardware status

// Query desired hardware active \ inactive state

DGS

// Set hardware active \ inactive state

```

Figure 3-1. Namespace with MXM Methods Example

## 3.3.1. Accessing MXM ACPI Methods via WMI

In order to allow access to the new MXM data from user mode and kernel software across Windows\*NT O/Ses the following headers shall be included in the graphics adapter namespace and any other devices that contain MXM methods in order to facilitate access via WMI. The GUID for WMI MXMX methods is:

```

{F6CB5C3C-9CAE-4EBD-B577-931EA32A2CC0}

```

The WMI GUIDs to use for **Notify** events are the same as those listed under Section 4.3.7.5 (MXM\_FUNC\_EVENTLIST).

WMI parameter Arg1 is used to specify which GPU's method is being called. The value of Arg1 is determined by calculating (0x100 + PCIe bus number for the GPU). Any related methods calling the motherboard chipset's integrated graphics should use Arg1 = 0x10.

For more details on using WMI to access ACPI methods refer to: http://www.microsoft.com/whdc/system/pnppwr/wmi/wmi-acpi.mspx.

In addition to the MXM-specific items and events, several events which are typically OS-supported but are key to MXM operation are included in the following ASL code and in the compiled MOF. If an OS does not support some of these events, they may need to be included under WMI1 in order to enable MXM software. Including them here also enables application level testing and verification. The GUIDs for these other events are also available under the section on MXM\_FUNC\_EVENTLIST.

Examples for this code are also provided in the SDK.

```

// placed within PCI Bus scope

Device (WMI1)

Name(_HID, "pnp0c14") // pnp0c14 is the ID assigned to WMI mapper

// use a unique UID for each instance

Name(_UID, "MXM2")

Description of data and events supported

// Methods GUID {F6CB5C3C-9CAE-4ebd-B577-931EA32A2CCD}

0x3C, 0x5C, 0xCB, 0xF6, 0xAE, 0x9C, 0xbd, 0x4e, 0xB5, 0x77, 0x93, 0x1E

0xA3, 0x2A, 0x2C, 0xC0,

0x4D, 0x58, // Object ID "MX" - method "WMMX"

// Instance Count

1,

// Flags (WMIACPI_REGFLAG_METHOD)

0x02,

// MOF data {05901221-D566-11d1-B2F0-00A0C9062910}

0x21, 0x12, 0x90, 0x05, 0x66, 0xd5, 0xd1, 0x11, 0xb2, 0xf0,

0x00, 0xa0, 0xc9, 0x06, 0x29, 0x10,

0x58, 0x4D, // Object ID "XM"

// Instance Count = 1

1,

0x00,

// Flags

// DISPLAY_HOTKEY, ACPI_NOTIFY_PANEL_SWITCH GUID

// Notify event 80 (fixed) - Hot-Key, use _DGS, _DCS ... etc.

// GUID (E06BDE62-EE75-48F4-A583-B23E69ABF891)

0x62, 0xDE, 0x6B, 0xE0, 0x75, 0xEE, 0xF4, 0x48, 0xA5, 0x83, 0xB2, 0x3E, 0x69, 0xAB,

0xF8, 0x91,

0x80, 0x00, 0x01, 0x08,

// DISPLAY_HOTplug, ACPI_NOTIFY_DEVICE_HOTPLUG

// Notify event 81 (fixed) - Hot-Plug, guery _DCS

// GUID {3ADEBD0F-0C5F-46ED-AB-2E-04-96-2B-4F-DC-BC}

0x0F, 0xBD, 0xDe, 0x3A, 0x5F, 0x0C, 0xED, 0x46, 0xAB, 0x2E, 0x04, 0x96, 0x2B, 0x4F,

0xDC, 0xBC,

```

```

0x81, 0x00, 0x01, 0x08,

// BRIGHTNESS_INC, ACPI_NOTIFY_INC_BRIGHTNESS_HOTKEY

// Notify event 86 (fixed) - Backlight Increase

// GUID {1E519311-3E75-4208-B05E-EBE17E3FF41F}

0x11, 0x93, 0x51, 0x1E, 0x75, 0x3E, 0x08, 0x42, 0xB0, 0x5E, 0xEB, 0xE1, 0x7E, 0x3F,

0xF4, 0x1F,

0x86, 0x00, 0x01, 0x08,

// BRIGHTNESS_DEC, ACPI_NOTIFY_DEC_BRIGHTNESS_HOTKEY

// Notify event 87 (fixed) - Backlight Decrease

// GUID {37F85341-4418-4F24-8533-38FFC7295542}

0x41, 0x53, 0xF8, 0x37, 0x18, 0x44, 0x24, 0x4F, 0x85, 0x33, 0x38, 0xFF, 0xC7, 0x29,

0x55, 0x42,

0x87, 0x00, 0x01, 0x08,

// ACPI_NOTIFY_POWER_LEVEL_D1

// Notify event D1 - Power State P0

// GUID {93263095-DA5F-46a0-8B1C-DB2F1F7D66AF}

0x95, 0x30, 0x26, 0x93, 0x5F, 0xDA, 0xA0, 0x46, 0x8B, 0x1C, 0xDB, 0x2F, 0x1F, 0x7D,

0x66, 0xAF,

0xD1, 0x00, 0x01, 0x08,

// ACPI_NOTIFY_POWER_LEVEL_D2

// Notify event D2 - Power State P1

// GUID {BE907006-D603-4714-9AE2-9DBA8997A805}

0x06, 0x70, 0x90, 0xBE, 0x03, 0xD6, 0x14, 0x47, 0x9A, 0xE2, 0x9D, 0xBA, 0x89, 0x97,

0xA8, 0x05,

0xD2, 0x00, 0x01, 0x08,

// ACPI_NOTIFY_POWER_LEVEL_D3

// Notify event D3 - Power State P2

// GUID {21D355E1-498D-4c1f-AE01-05CEF8DD053F}

0xE1, 0x55, 0xD3, 0x21, 0x8D, 0x49, 0x1F, 0x4C, 0xAE, 0x01, 0x05, 0xCE, 0xF8, 0xDD,

0x05, 0x3F,

0xD3, 0x00, 0x01, 0x08,

// ACPI_NOTIFY_POWER_LEVEL_D4

// Notify event D4 - Power State P3

// GUID {EDBCEDF1-BBC9-420e-A3C0-322B1D37C3AA}

0xF1, 0xED, 0xBC, 0xED, 0xC9, 0xBB, 0x0E, 0x42, 0xA3, 0xC0, 0x32, 0x2B, 0x1D, 0x37,

0xC3, 0xAA,

0xD4, 0x00, 0x01, 0x08,

// ACPI_NOTIFY_POWER_LEVEL_D5

// Notify event D5 - Power State P4

// GUID {377E84E1-13DE-41fb-A096-0F08528BA689}

0xE1, 0x84, 0x7E, 0x37, 0xDE, 0x13, 0xFB, 0x41, 0xA0, 0x96, 0x0F, 0x08, 0x52, 0x8B,

0xA6, 0x89,

0xD5, 0x00, 0x01, 0x08

})

// Method Execution

// MXM Native Methods are called via WMMX Index

// ONLY include the methods that you actually have !

Method (WMMX, 3)

CreateDWordField(Arg2, 0, FUNC)

// Get the function name

If (LEqual(FUNC, 0x4D53445F))

// "_DSM"

If (LGreaterEqual(SizeOf(Arg2), 28))

CreateField(Arg2, 32, 128, MUID)

CreateDWordField(Arg2, 20, REVI)

CreateDWordField(Arg2, 24, SFNC)

CreateDWordField(Arg2, 28, ARGD)

If (LEqual (And (Argl, OxFF)), DGPU_SCOPE.GBUS())) {

Return(DGPU_SCOPE._DSM(MUID, REVI, SFNC, ARGD))

If (LEqual (And (Argl, OxFF)), DGPU2_SCOPE.GBUS())) {

```

```

Return(DGPU2_SCOPE._DSM(MUID, REVI, SFNC, ARGD))

Return (0)

// Compiled form of the associated MOF declaration

Name (WQXM, Buffer() (

0x46,0x4F,0x4D,0x42,0x01,0x00,0x00,0x00,0xCC,0x05,0x00,0x00,0xFC,0x30,0x00,0x00,

0x44,0x53,0x00,0x01,0x1A,0x7D,0xDA,0x54,0x18,0xD2,0x97,0x00,0x01,0x06,0x18,0x42,

0x10,0x19,0x10,0x8A,0xE6,0x80,0x42,0x04,0x92,0x43,0xA4,0x30,0x30,0x28,0x0B,0x20,

0x86,0x90,0x0B,0x26,0x26,0x40,0x04,0x84,0xBC,0x0A,0xB0,0x29,0xC0,0x24,0x88,0xFA,

0xF7,0x87,0x28,0x09,0x0E,0x25,0x04,0x42,0x12,0x05,0x98,0x17,0xA0,0x5B,0x80,0x61,

0x01,0xB6,0x05,0x98,0x16,0xE0,0x18,0x92,0x4A,0x03,0xA7,0x04,0x96,0x02,0x21,0xA1,

0x02,0x94,0x0B,0xF0,0x2D,0x40,0x3B,0xA2,0x24,0x0B,0xB0,0x0C,0x23,0x02,0x8F,0x82,

0xA1,0x71,0x68,0xEC,0x30,0x2C,0x13,0x4C,0x83,0x38,0x8C,0xB2,0x91,0x45,0x60,0xDC,

0x4E,0x05,0xC8,0x15,0x20,0x4C,0x80,0x78,0x54,0x61,0x34,0x07,0x45,0xE0,0x42,0x63,

0x46,0x69,0x8F,0x02,0xAC,0x8E,0x42,0x93,0x4A,0x60,0xF7,0x02,0x34,0x0A,0xD0,0x26,

0xC0,0xA1,0x00,0x85,0x02,0xAC,0x61,0xC8,0x19,0x84,0x6C,0x61,0x0B,0xA3,0x41,0x01,

0x16,0x51,0x34,0x82,0xB3,0xA8,0x78,0x4E,0x42,0x09,0x68,0x6F,0x08,0xC2,0x33,0x66,

0x63,0x78,0x42,0x0C,0x52,0x19,0x86,0x20,0xE2,0x46,0x38,0x96,0xF6,0x07,0x41,0xE4,

0x2B, 0x18, 0x37, 0x8B, 0x34, 0x1A, 0xD4, 0x58, 0x13, 0x1C, 0xBB, 0x47, 0x73, 0xC2, 0x9D, 0x0B,

0x90,0x3E,0x37,0x81,0x1C,0xDD,0x69,0xD4,0x39,0x68,0x32,0x3C,0x86,0x95,0xE0,0x3F,

0xC0,0xA7,0x00,0xBC,0x6B,0x40,0x4D,0xFF,0xE0,0x99,0x20,0x38,0xD4,0x10,0x3D,0xEA,

0x70,0x27,0x70,0x5E,0x47,0xC2,0x20,0x8E,0xE8,0xB8,0xB1,0xB3,0x3A,0x99,0x83,0x2E,

0x55,0x80,0xD9,0x03,0x80,0x06,0x97,0xE0,0xB4,0xCF,0x24,0xF4,0x7B,0xC0,0xF9,0xF4,

0x3C,0x36,0x36,0x08,0xD4,0xC8,0xFC,0xFF,0x87,0xF6,0x20,0x4F,0x2B,0x66,0xC8,0x67,

0x81,0xC3,0x62,0x62,0x21,0xB4,0x49,0x8D,0x07,0x08,0x1C,0x00,0x1E,0x0D,0x22,0xBC,

0x19,0x78,0xBE,0x26,0x18,0x14,0x42,0x4E,0xC6,0x83,0x12,0x73,0x3E,0x20,0x73,0x09,

0xF1,0x10,0x70,0x0C,0x31,0x82,0x9E,0x51,0xD1,0xC8,0x9A,0x88,0xCF,0x00,0x1E,0xB7,

0x65,0x81,0x50,0x02,0x03,0xFB,0xDC,0xF0,0x0E,0x61,0x58,0xDC,0x68,0x02,0xFB,0x7C,

0x61,0x81,0x83,0x42,0xC1,0xFA,0xAE,0x10,0xF3,0x79,0xE0,0x38,0x0F,0xD8,0xC2,0x27,

0x4A, 0x80, 0x0F, 0xC9, 0xA3, 0x81, 0x37, 0x48, 0xF8, 0xD6, 0x8F, 0x00, 0x04, 0xF8, 0x89, 0xC1,

0x04,0x96,0x07,0x8C,0x1E,0xA5,0xFD,0x0A,0x40,0x08,0xFE,0x62,0xF1,0x14,0xF0,0x3A,

0x10,0xE1,0x58,0x60,0x8A,0x1C,0x1B,0x1A,0x9E,0x1F,0x1C,0xA2,0x47,0x3D,0x97,0xF0,

0x47,0x13,0xE5,0x14,0x0E,0xC7,0x47,0x0E,0x23,0x84,0x7F,0xD2,0x78,0xF2,0xB0,0xE6,

0x3B,0x80,0xA6,0xF4,0x16,0xF0,0xFE,0xE0,0x11,0x60,0x04,0x48,0x38,0x9A,0x60,0x22,

0x9F,0x4E,0x40,0xF5,0xFF,0x3F,0x9D,0x00,0xA6,0xA6,0x1C,0xF4,0xED,0xE4,0x29,0x22,

0x50,0x94,0x20,0x2F,0x01,0x6F,0x25,0x41,0x22,0xBC,0x97,0x3C,0x99,0x3C,0x9D,0x58,

0xDC,0x29,0x45,0x18,0x51,0x8E,0x3E,0x50,0x98,0x17,0x83,0xF7,0x13,0x43,0x06,0x09,

0xEB, 0x79, 0xC4, 0x8A, 0x13, 0x30, 0x58, 0x94, 0x37, 0x94, 0xA7, 0x13, 0x16, 0xF2, 0xA1, 0x21,

0x0D, 0xA7, 0x13, 0x80, 0x02, 0xFF, 0xFF, 0xD3, 0x09, 0xFC, 0xA8, 0xA7, 0x13, 0xF4, 0x70, 0x7D,

0xCA, 0xC0, 0x20, 0x1F, 0x90, 0x4F, 0x1D, 0x3E, 0x07, 0x9C, 0x86, 0x8F, 0x27, 0x18, 0x51, 0xC7,

0x13,0xD4,0xE9,0xC1,0xC7,0x13,0x76,0x3E,0x38,0x8B,0xC7,0x00,0x9F,0x4E,0x30,0xF7,

0x04,0x9F,0x4E,0xC0,0x36,0x1A,0x18,0xC7,0x13,0xF0,0x1D,0x5D,0x70,0xC7,0x13,0x30,

0x0C, 0x06, 0xC6, 0xF9, 0x04, 0x78, 0x8C, 0x17, 0x77, 0x0C, 0xF0, 0x10, 0xF8, 0x00, 0x1E, 0x37,

0x4E,0xCF,0x4A,0x27,0x85,0x3C,0x89,0xF0,0x41,0x61,0x0E,0x2C,0xC0,0xE1,0xFF,0x7F,

0x60,0x01,0x4C,0xDD,0x0F,0x4E,0xF9,0x79,0xC5,0x17,0x16,0x23,0xBF,0xA3,0xBC,0xA8,

0xC4,0x38,0xF0,0x77,0x95,0x28,0x1E,0xC1,0x9B,0x4A,0xB4,0x60,0x0F,0x2C,0x3E,0xAE,

0xF8,0x88,0x66,0xBC,0x58,0x87,0xF1,0xEA,0x62,0xA4,0x28,0x31,0xE3,0xBD,0xAC,0x19,

0xE2,0x81,0x05,0x60,0xC3,0xFF,0xFF,0xC0,0x02,0x4C,0xAE,0x41,0x0F,0x2C,0xC0,0x78,

0x34,0xEC,0xC0,0x02,0x4C,0x07,0xC3,0x0E,0x2C,0x80,0xCB,0xFF,0xFF,0x81,0x05,0x30,

0x75,0x20,0xF5,0x5D,0x25,0xC6,0x33,0x29,0x43,0x78,0x51,0x79,0x4F,0xF3,0x81,0x8D,

0x5F,0x0D,0x7C,0x30,0x78,0x5B,0x33,0x48,0xA4,0x07,0x16,0x5F,0x5D,0x0C,0x11,0x34,

0x62,0x8C,0xA8,0x0F,0x2C,0x0F,0x6E,0xC6,0x89,0xF1,0xC0,0x02,0xB0,0xE1,0xFF,0x7F,

0x60,0x01,0x26,0x57,0xA1,0x07,0x16,0x60,0x3C,0x1A,0x76,0x60,0x01,0xA6,0x83,0x61,

0x07,0x16,0xC0,0xE5,0xFF,0xFF,0xC0,0x06,0xB8,0xBA,0xA2,0x3C,0xA1,0xFA,0x9E,0x12,

0xE5,0x15,0xC5,0xB7,0x15,0x83,0xF8,0xB6,0xE2,0x83,0x9A,0xCF,0x06,0x0F,0xAC,0xO6,

0x64,0x07,0x56,0x43,0x3C,0xB5,0x1A,0xE1,0x09,0x20,0x78,0xB8,0x13,0x09,0x16,0xE1,

0xD1,0xC5,0x07,0x16,0x80,0x0D,0xFF,0xFF,0xO3,0x0B,0x30,0xB9,0x09,0x3C,0xB0,0x00,

0xE3,0xD1,0xB0,0x03,0x0B,0x30,0x1D,0x0C,0x3B,0xB0,0x00,0x2E,0xFF,0xFF,0x07,0x16,

0xC0,0xD4,0x71,0xCD,0x87,0x82,0x17,0xA2,0x18,0x81,0x7D,0x5B,0x33,0xDA,0xBB,0xBA,

0x0F, 0xAC, 0x7C, 0x1C, 0xC1, 0x1E, 0x58, 0x7C, 0xC1, 0x78, 0x6A, 0x39, 0xFC, 0x78, 0xBE, 0xB2,

0x1A, 0xEF, 0x69, 0xCD, 0xC7, 0x83, 0x38, 0x11, 0x23, 0x04, 0x7E, 0x60, 0x03, 0xF8, 0xF0, 0xFF,

0x3F, 0xB0, 0x00, 0x8F, 0x83, 0xC0, 0x03, 0x2B, 0x30, 0x1E, 0x0D, 0x3F, 0xB0, 0x00, 0xCF, 0xC1,

0xF0,0x03,0x0B,0xE0,0xF2,0xFF,0x7F,0x60,0x01,0x4C,0xDD,0x51,0x0D,0x1A,0xF6,0x19,

0x25,0x44,0x84,0x67,0x94,0x17,0x15,0x63,0x44,0x79,0x56,0xF3,0x08,0x62,0x3D,0x17,

0x3C, 0xB0, 0x19, 0xF1, 0xE0, 0x83, 0x3E, 0x1E, 0x44, 0xF1, 0x85, 0xC5, 0x38, 0x2F, 0x2D, 0x51,

0x22,0x04,0x8C,0xE2,0x73,0xAB,0x0F,0x2C,0x00,0x1B,0xFE,0xFF,0x07,0x16,0x60,0x72,

0x0E,0x61,0x07,0x16,0x60,0x3B,0x1A,0x76,0x60,0x01,0xA6,0x03,0x60,0x07,0x16,0xC0,

```

```

0xE5,0xFF,0xFF,0xC0,0x02,0x98,0x3A,0x0F,0xBC,0xA8,0x84,0x79,0x42,0x78,0x44,0xF5,

0x31,0xDD,0xB7,0x15,0x83,0x3F,0xA5,0x84,0x8A,0xE2,0x71,0x44,0x7A,0x0F,0x88,0xF2,

0xBE, 0xE2, 0x41, 0xC4, 0xF3, 0x59, 0xC5, 0x27, 0x02, 0x9F, 0x5E, 0x0D, 0x19, 0x21, 0x90, 0x8F,

0xEC, 0x3E, 0xB0, 0x00, 0x6C, 0xF8, 0xFF, 0x1F, 0x58, 0x80, 0xC9, 0x39, 0xE0, 0x81, 0x05, 0x18,

0x8F, 0x86, 0x1D, 0x58, 0x80, 0xE9, 0x60, 0xD8, 0x81, 0x05, 0x70, 0xF9, 0xFF, 0x3F, 0xB0, 0x00,

0xA6,0x86,0xFB,0x90,0xE6,0x5B,0x80,0x41,0xDE,0x52,0x7D,0x51,0x89,0x13,0xC8,0xF0,

0x0F,0x2C,0xBE,0x1A,0x78,0x1A,0x0F,0x2C,0x3E,0x19,0x84,0x7A,0x65,0xF5,0x5D,0xC1,

0x08, 0xEF, 0xAC, 0x3E, 0x1E, 0xF8, 0xC0, 0x16, 0x2B, 0x46, 0xBC, 0x08, 0x0F, 0x2C, 0x00, 0x1B,

0xFE, 0xFF, 0x07, 0x16, 0x60, 0x72, 0x59, 0xF0, 0x81, 0x05, 0xF8, 0x8E, 0x86, 0x1D, 0x58, 0x80,

0xE9,0x60,0xD8,0x81,0x05,0x70,0xF9,0xFF,0x3F,0xB0,0x00,0xA6,0x4E,0x28,0x46,0x38,

0xDF, 0x77, 0xB4, 0xC8, 0x0F, 0x6C, 0x0C, 0x22, 0x54, 0xBC, 0x30, 0x0F, 0x2C, 0xBE, 0xAF, 0x59,

0xF1,0x81,0x85,0xCC,0xC1,0xF7,0x56,0x83,0xBC,0xB9,0x84,0x88,0xFB,0xB6,0xF6,0x86,

0xF0,0xD6,0x6E,0xB4,0x58,0xCF,0xAC,0x3E,0xB0,0x00,0x6C,0xF8,0xFF,0x1F,0x58,0x80,

0xC9,0x51,0xE0,0x81,0x05,0x18,0x8F,0x86,0x1D,0x58,0x80,0xE9,0x60,0xD8,0x81,0x05,

0x70,0xF9,0xFF,0x3F,0xB0,0x03,0xAE,0x0E,0x08,0xC7,0x1B,0xF7,0x25,0xC5,0x57,0x62,

0x5F,0xD4,0x3C,0xF0,0x08,0xAF,0xAC,0xEC,0xBC,0x72,0x04,0x0F,0xEC,0xC6,0x7B,0x5B,

0x09,0x16,0xCA,0x77,0x17,0xDF,0x56,0x8C,0x1A,0x29,0xF0,0xA3,0x9B,0xF1,0x9F,0xE0,

0x7D,0x60,0x01,0xD8,0xF0,0xFF,0x3F,0xB0,0x00,0x8F,0xA3,0xB0,0x0F,0x2C,0xC0,0x77,

0x34,0xFC,0xC0,0x02,0x3C,0x07,0xC3,0x0F,0x2C,0x80,0xCB,0xFF,0xFF,0x81,0x0D,0x70,

0x75,0x40,0x8B,0x1A,0x27,0xC6,0x1B,0xC1,0x9B,0xC5,0x8B,0x9A,0xAF,0xA9,0x3E,0xB3,

0xF9,0xC0,0xE2,0x6B,0x80,0xA1,0x8C,0xF6,0xE0,0x66,0x88,0x78,0xBE,0xAB,0x18,0xFB,

0xC9,0xCD,0x08,0x91,0xC2,0xBC,0x03,0xBC,0xB4,0xF8,0xC0,0xO2,0xB0,0xE1,0xFF,0x7F,

0x60,0x03,0x26,0x77,0x41,0x1F,0x58,0x80,0xED,0x64,0xD8,0x81,0x05,0x98,0x0E,0x86,

0x1F, 0x58, 0x00, 0x27, 0x0A, 0x6D, 0xFA, 0xD4, 0x68, 0xD4, 0xAA, 0x41, 0x99, 0x1A, 0x65, 0x1A,

0xD4,0xEA,0x53,0xA9,0x31,0x63,0xC7,0x14,0x07,0x7C,0x08,0xE8,0x44,0x60,0x79,0xCF,

0x06,0x81,0x58,0x06,0x85,0x40,0x2C,0xFD,0xD5,0x22,0x10,0x07,0x07,0xD1,0xFF,0x1F,

0xC4,0x11,0x9F,0x1C,0x02,0x23,0x26,0xC0,0x28,0x08,0x8D,0xA8,0x02,0x8C,0xDA,0x00,

0xA3,0x20,0x34,0xA2,0x0E,0x30,0x6A,0x04,0x8C,0x82,0xD0,0x88,0x4A,0xC0,0xA8,0x15,

0x30,0x0A,0x42,0x23,0x6A,0x01,0xA3,0x66,0xC0,0x28,0x08,0x8D,0xA8,0x06,0x8C,0xDA,

0x01,0xA3,0x20,0x34,0xA2,0x1E,0x30,0x6A,0x08,0x8C,0x82,0xD0,0x88,0x8A,0xC0,0xA8,

0x25,0x30,0x0A,0x42,0x23,0x6A,0x02,0xA3,0xA6,0xC0,0x28,0x08,0x8D,0xA8,0x0A,0x8C,